- English

- French

- German

- Portuguese

- Spanish

- Russian

- Japanese

- Korean

- Arabic

- Greek

- German

- Turkish

- Italian

- Danish

- Romanian

- Indonesian

- Czech

- Afrikaans

- Swedish

- Polish

- Basque

- Catalan

- Esperanto

- Hindi

- Lao

- Albanian

- Amharic

- Armenian

- Azerbaijani

- Belarusian

- Bengali

- Bosnian

- Bulgarian

- Cebuano

- Chichewa

- Corsican

- Croatian

- Dutch

- Estonian

- Filipino

- Finnish

- Frisian

- Galician

- Georgian

- Gujarati

- Haitian

- Hausa

- Hawaiian

- Hebrew

- Hmong

- Hungarian

- Icelandic

- Igbo

- Javanese

- Kannada

- Kazakh

- Khmer

- Kurdish

- Kyrgyz

- Latin

- Latvian

- Lithuanian

- Luxembou..

- Macedonian

- Malagasy

- Malay

- Malayalam

- Maltese

- Maori

- Marathi

- Mongolian

- Burmese

- Nepali

- Norwegian

- Pashto

- Persian

- Punjabi

- Serbian

- Sesotho

- Sinhala

- Slovak

- Slovenian

- Somali

- Samoan

- Scots Gaelic

- Shona

- Sindhi

- Sundanese

- Swahili

- Tajik

- Tamil

- Telugu

- Thai

- Ukrainian

- Urdu

- Uzbek

- Vietnamese

- Welsh

- Xhosa

- Yiddish

- Yoruba

- Zulu

Current Situation Of Tantalum Target Forging

2024-01-05 18:00:06

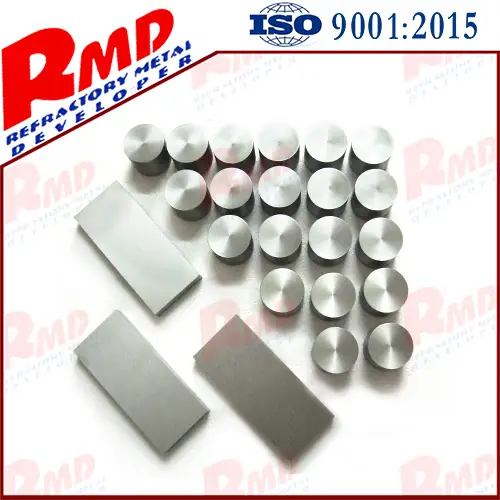

For tantalum target forging. Physical vapor deposition (PVD) is one of the most critical processes in the production of semiconductor chips. The purpose of PVD is to deposit metal or metal compounds on silicon wafers or other substrates in the form of thin films, and then, through the combination of photolithography, corrosion and other processes, to eventually form the complex wiring structure in semiconductor chips. Physical vapor deposition is accomplished by sputtering machine, and sputtering target material is a very important key consumable material used in the above mentioned process. Common sputtering targets have high purity Ta, as well as non-ferrous metals such as Ti, Al, Co and Cu. The production of sputtering target is developed at the same time as the semiconductor production process, so the information of its production technology and application is extremely rare. Moreover, due to the high investment, high risk and high competitiveness of semiconductor technology, the technical and market information of target materials closely related to its competitiveness (determined by cost and technology) is extremely confidential.

Currently, only two countries in the world, Japan and the United States, have the production capacity to produce advanced sputtering targets for semiconductors. However, Taiwan and South Korea still rely on the import of targets from the United States and Japan despite their strong semiconductor production capacity.

With the rapid development of semiconductor technology, the integration degree is higher and higher, monocrystalline silicon chip integrated device for exponential growth per unit area, but also more and more big, silicon wafer size wiring width more and more thin, therefore the demands of the size of sputtering target materials is becoming more and more big, also calls for more refined microstructure, the forefront of the semiconductor technology is 12 "wafer very large scale integrated circuit manufacturing technology. An 8 "target is the target that is needed to produce the 8" wafer. Although the current leading edge of semiconductor integrated circuits in the world is 12nm wafer 90nm technology, and 65nm, 45nm and 32nm technology are being developed, the current large-scale production in China is represented by smic with 8mm wafer 0.13-0.18um (130_180nm) technology. As the chip size (8 inches) increased from 200 mm to 300 mm (12 inches) and the corresponding pie shoot Dr. Gerba material size must increase in order to meet the basic requirements of PVD coating, at the same time, the line width from (130-180 nm) reduce to 90 _45nm, based on the electrical conductivity of the conductor and matching performance of barrier layer, the sputtering target materials will also be from ultra high purity Al/Ti system into ultra high purity Cu/Ta, Ta in semiconductor sputtering target material industry the importance of more and more big, at the same time demand is also more and more big. After sputtering on silicon film thickness uniformity, it is very important for the final product, depending on the internal structure and texture orientation of tantalum target, uniform grain size, grain crystallization orientation towards the same target, will cause the sputtering grain sputtering in the sputtering rate reaching the same trajectory approaching the same distribution, sputtering atom Angle, so that you will get uniform coating film thickness, and at the same time of tantalum target material utilization rate is greatly increased. At present, China's production of large specification (8 inches or 12 inches) tantalum target technology is still in the immature stage. The main drawback of the existing technology is that for the ingots of large size (diameter greater than 200mm), the original grain cannot be effectively and uniformly broken after forging, resulting in belt and uneven grain and other defects.